NEWS

回首:砥砺耕耘,孜孜不息,

成为本土RISC-V CPU IP的领军企业

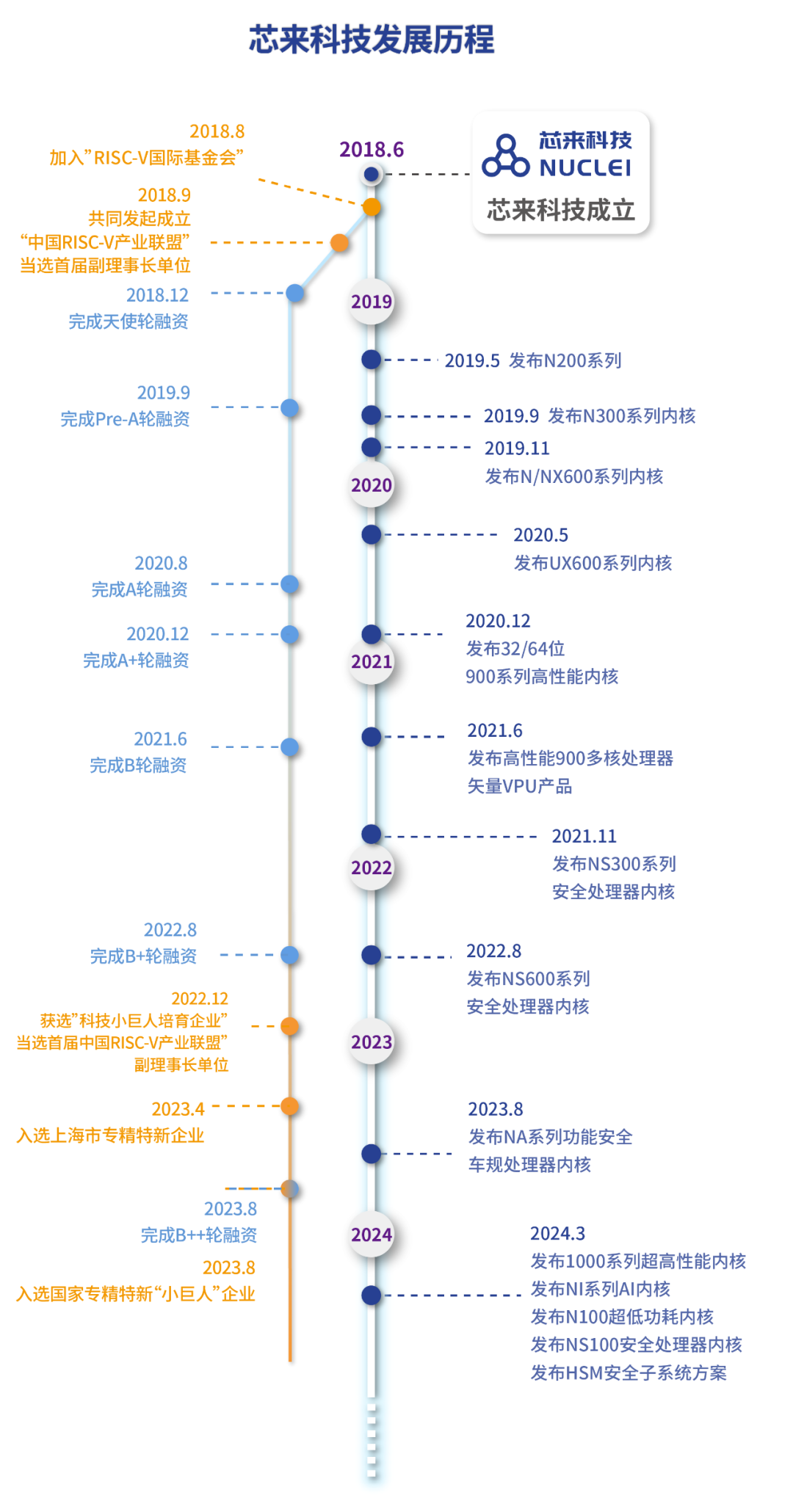

2024年6月,芯来科技将迎来成立6周年。芯来科技自创立伊始之时,便是本土最早致力于RISC-V CPU IP的企业之一,六年以来,芯来科技不忘初心,矢志不渝,一直专注于RISC-V CPU IP及相应平台方案的研发,发展成为了本土RISC-V CPU IP的领军企业。

1.1

六年砥砺耕耘,构建了全球最完备的RISC-V IP产品货架之一

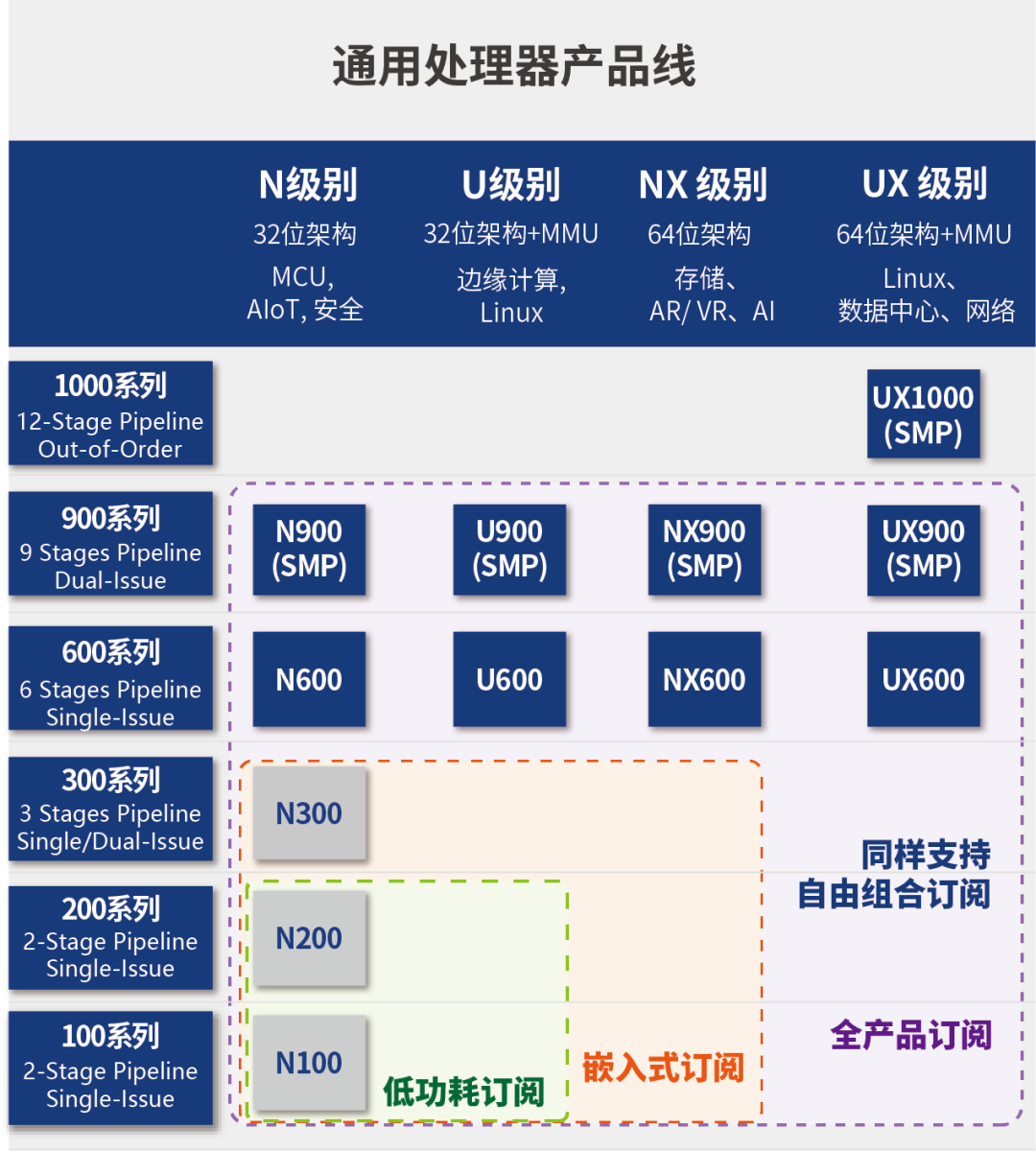

回首2018年,RISC-V CPU IP在本土起步之时,相比于国际上要滞后2-3年的时间。芯来科技从零开始,完全自研,通过六年的砥砺耕耘,基本上追平了与国际上的差距,构建了全球最完备的RISC-V IP产品货架之一,打造了N/U、NX/UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。

1.2

六年孜孜不息,成为全球范围内客户数量最多的RISC-V IP供应商之一

六周年之际

全面推出“RISC-V IP 2.0模式”

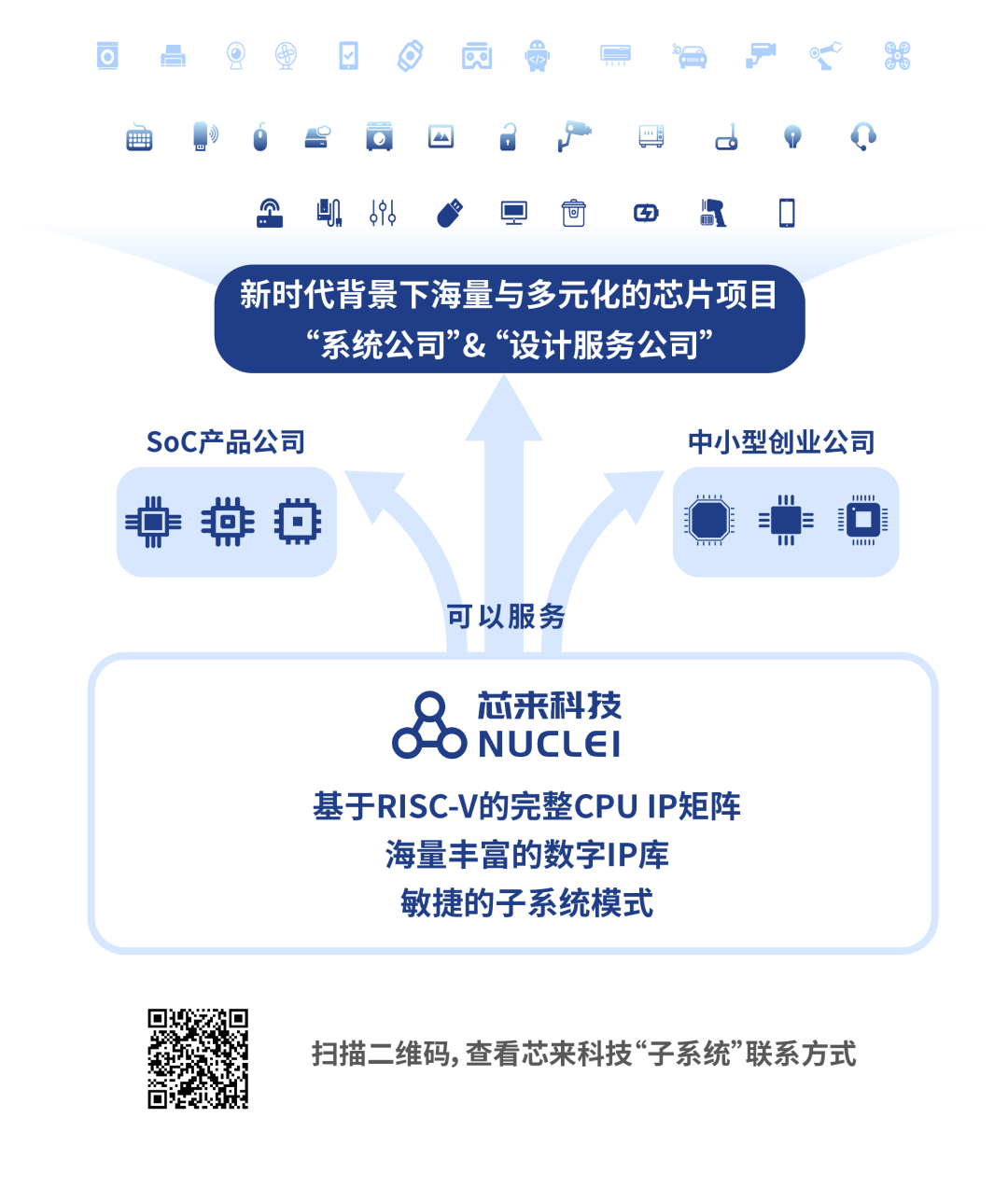

即便如此,在通过六年来与国内数百家客户的合作交流中,我们发现在本土市场,仍然存在一些明显的产业痛点,为了缓解这些痛点,在成立六周年之际,芯来科技全面推出新型的“RISC-V IP 2.0模式”,包含两方面内容:

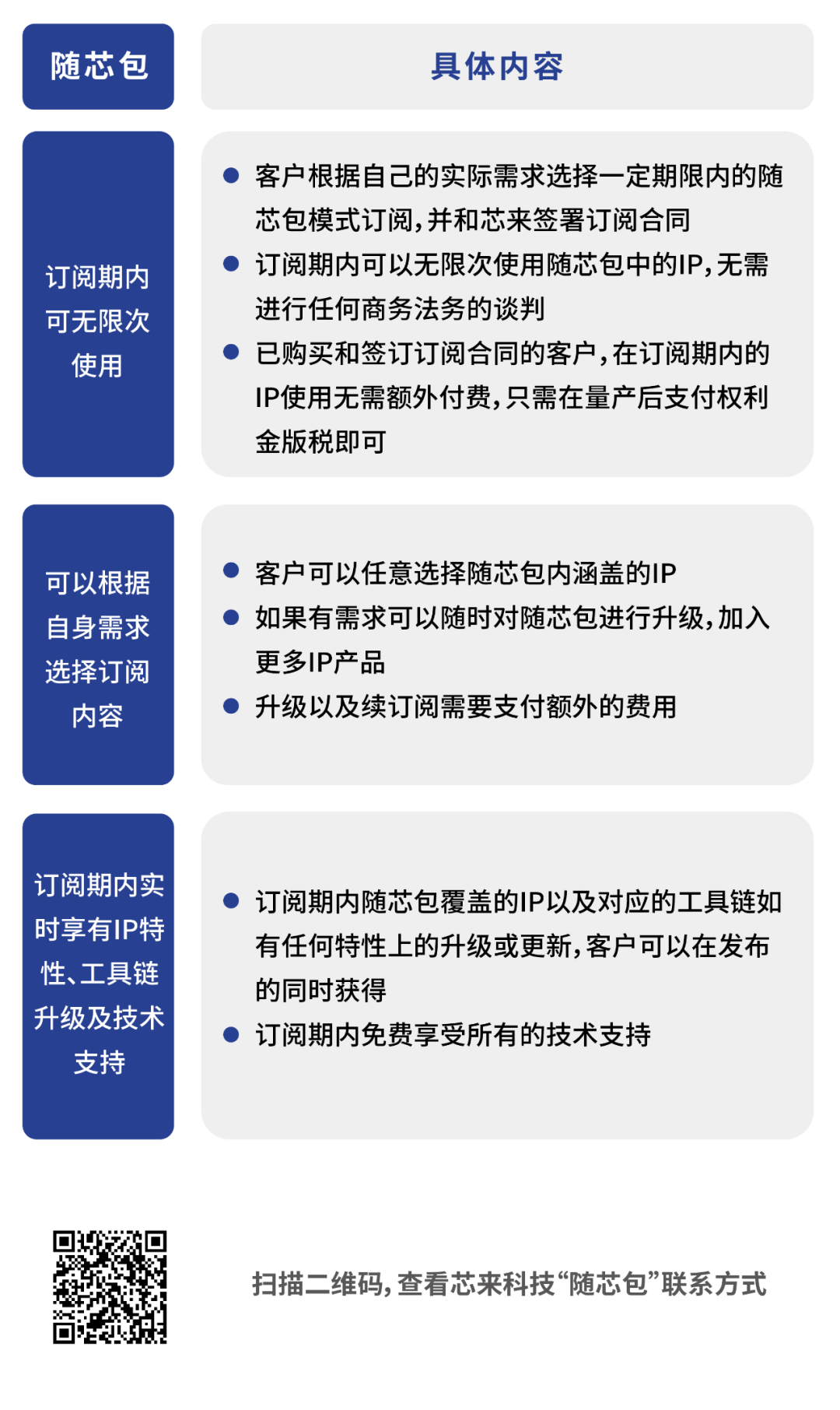

① RISC-V IP 2.0之——"随芯包"模式:

旨在降低采纳CPU IP的门槛与成本;

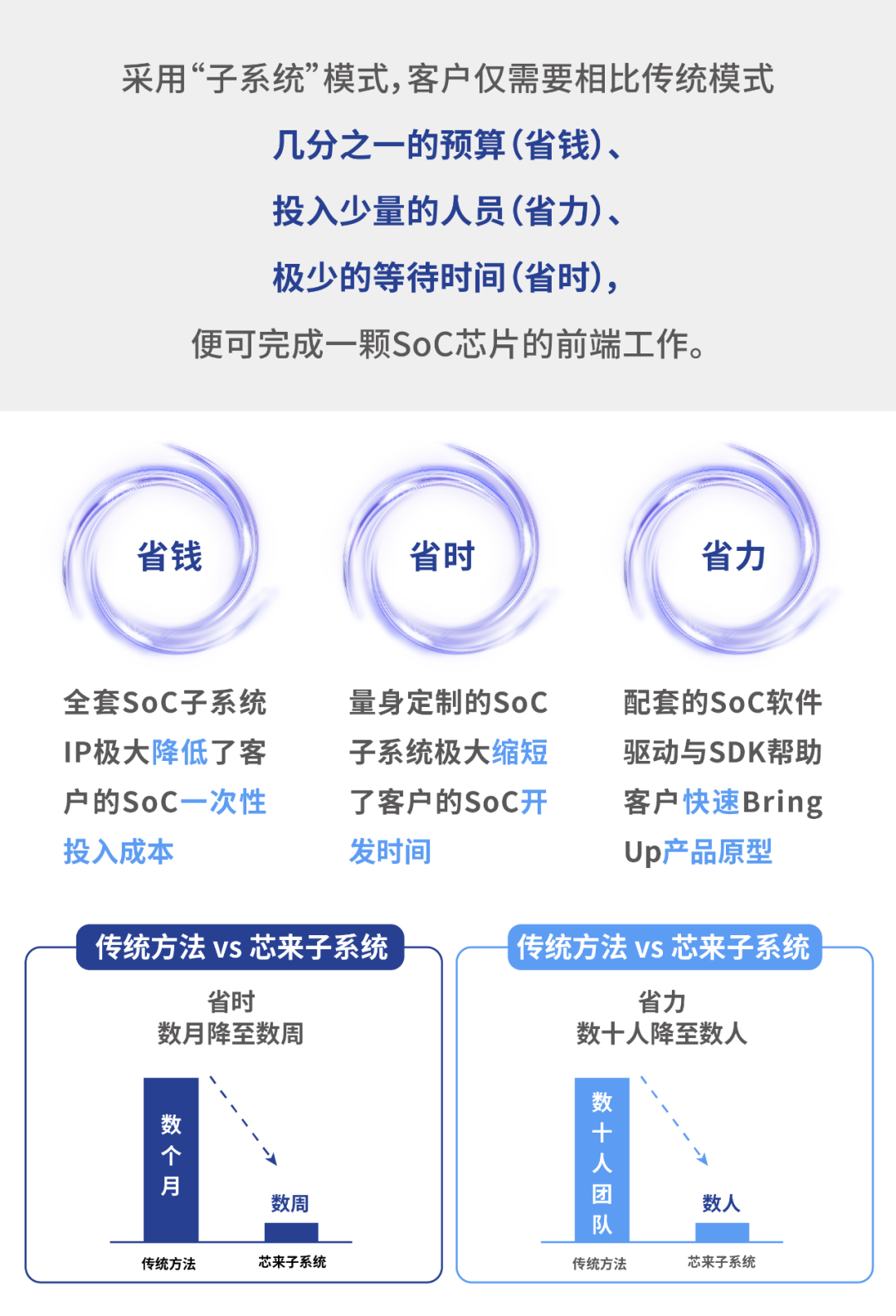

② RISC-V IP 2.0之——"子系统"模式:

旨在通过SoC整体IP化的方式,帮助本土客户在SoC层面省钱省时省力,颠覆式地降低SoC项目的设计成本。

▼ 接下来,我们对这两方面进行详细介绍:

2.1

RISC-V IP 2.0之——“随芯包”

为什么推出“随芯包”模式?

为此,芯来科技在六周年之际,特推出RISC-V CPU IP“随芯包”模式,将CPU IP从传统的“按项目授权”模式,提升到“订阅式”模式,助力本土设计公司更高效的完成CPU IP的采纳与授权过程,大幅缩减CPU IP的授权成本和时间成本:

“随芯包”模式提供的内容是什么?

芯来科技将N100、N200、N300、N600、N900;U600、U900 (支持MMU) 、NX600、NX900;UX600、UX900 (支持 MMU),纳入“随芯包”订阅模式的范畴。

这些IP型号是最成熟和通用的CPU IP型号,且饱受市场验证,将能够满足本土绝大多数SoC项目的CPU IP需求:

“随芯包”模式如何操作?

2.2

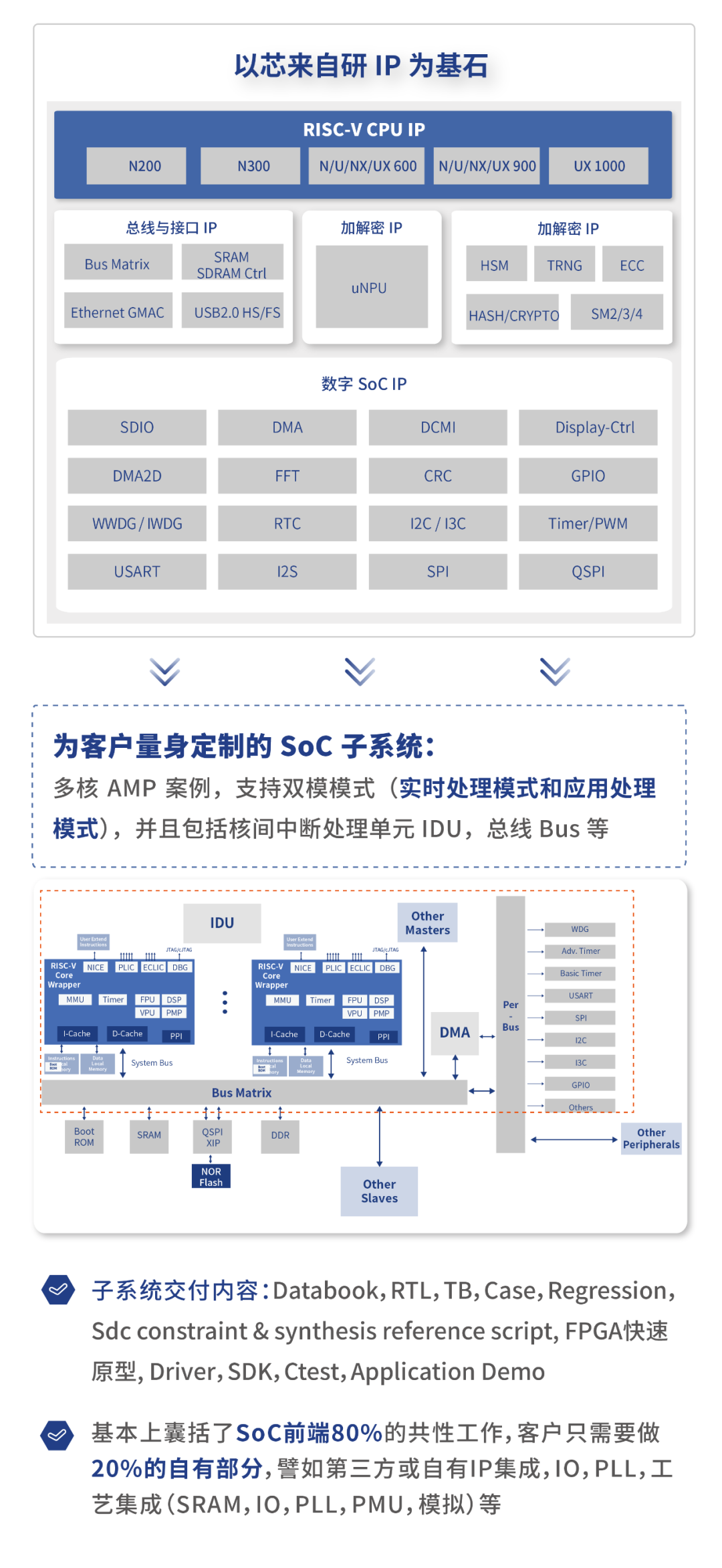

RISC-V IP 2.0之——“子系统”

为什么推出“子系统”模式?

为此,芯来科技在六周年之际,特推出“子系统”模式,将“分离IP”授权模式,提升到“SoC子系统”定制与授权模式。

“子系统”模式提供的内容是什么?

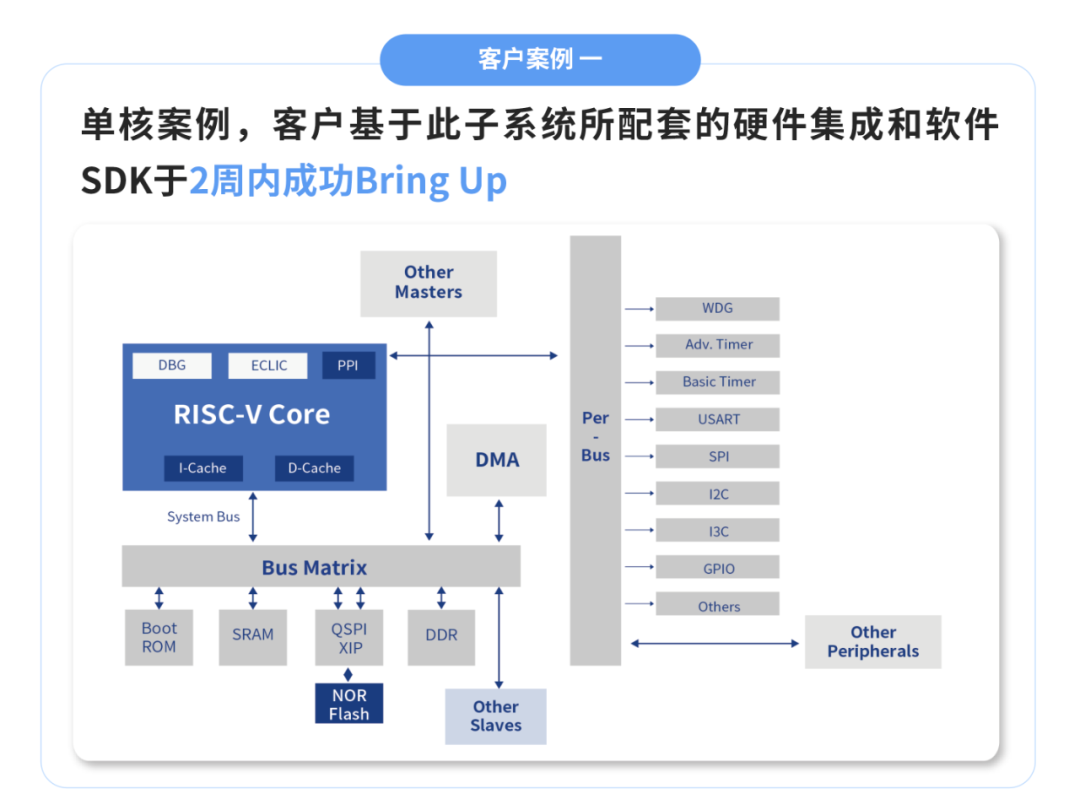

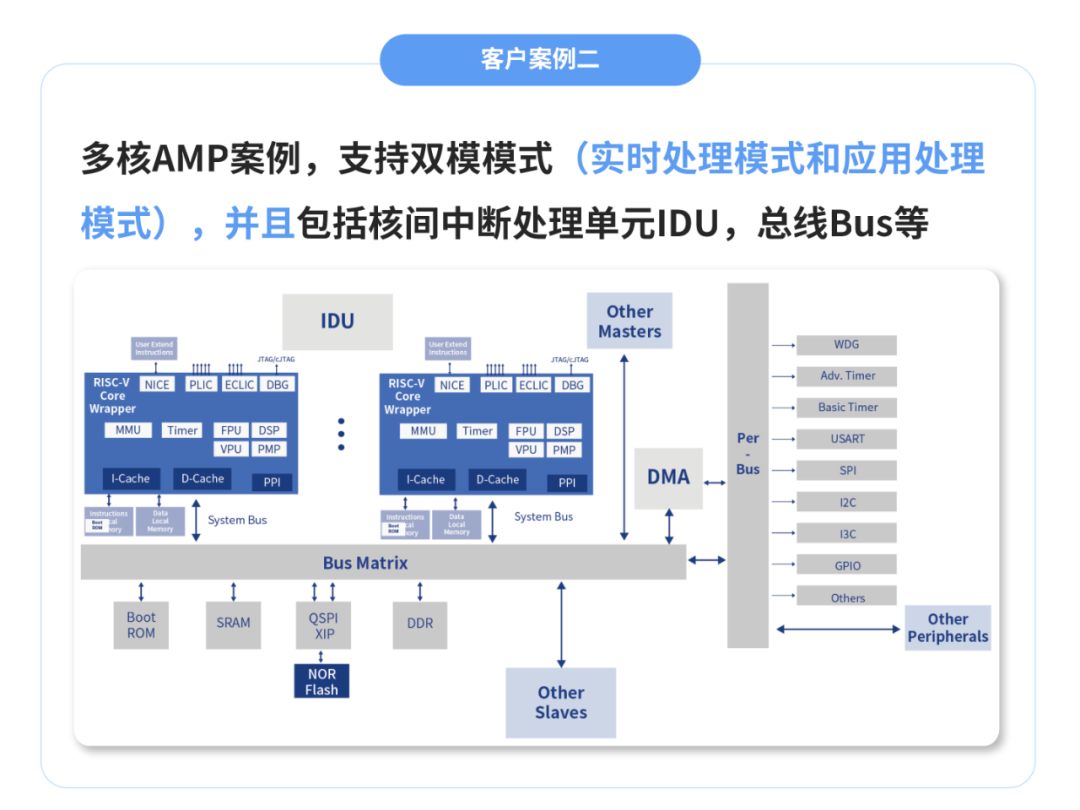

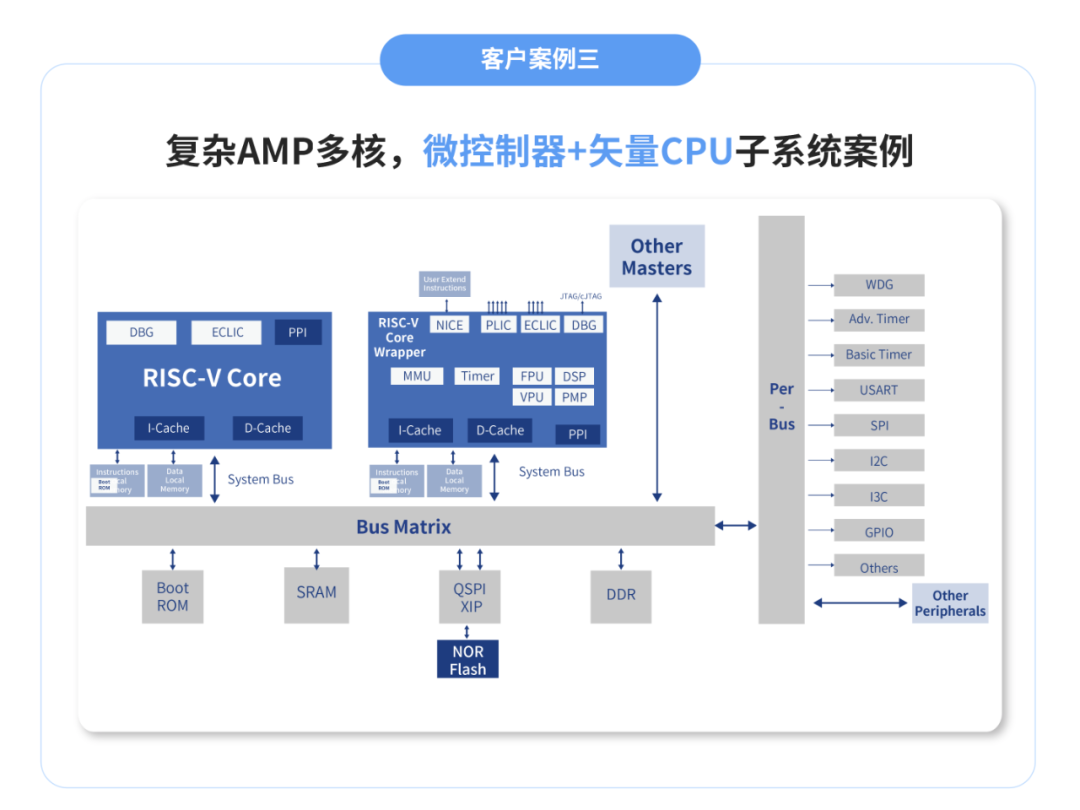

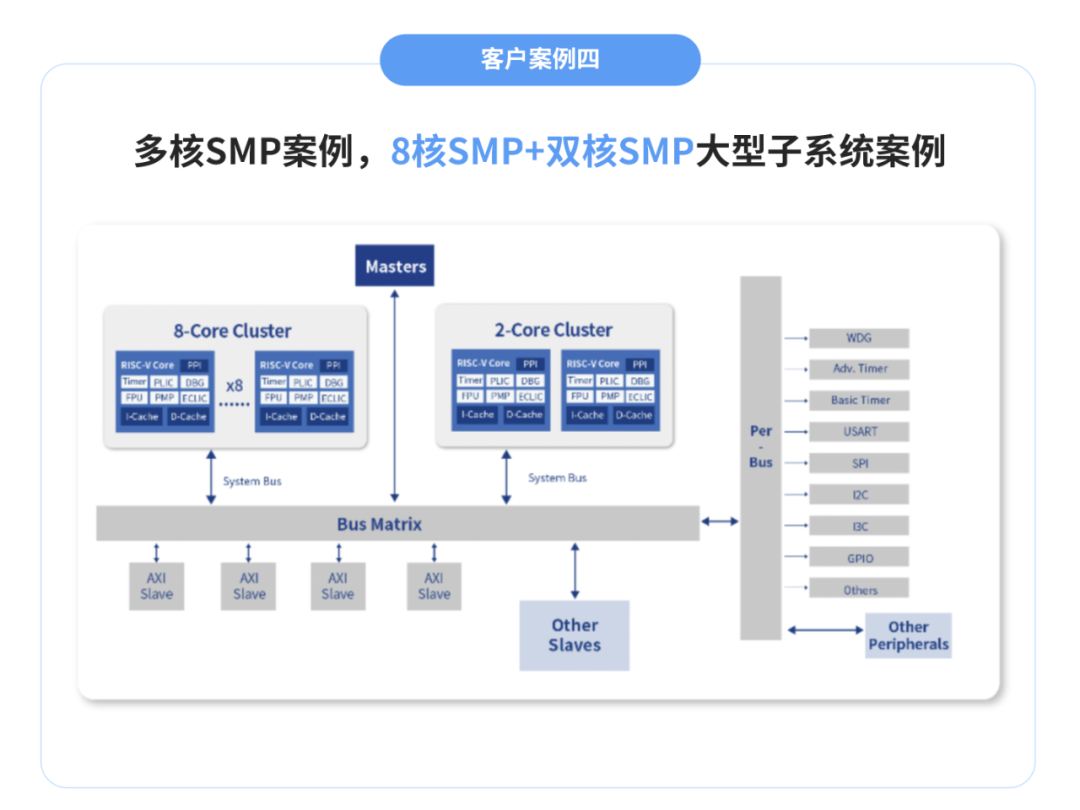

“子系统”模式面向客户推出的不再是单独的CPU IP,也不是一个个独立的SoC IP,而是一个完整的SoC子系统,如下图所示:

超过80+子系统客户

<< 滑动查看 >>

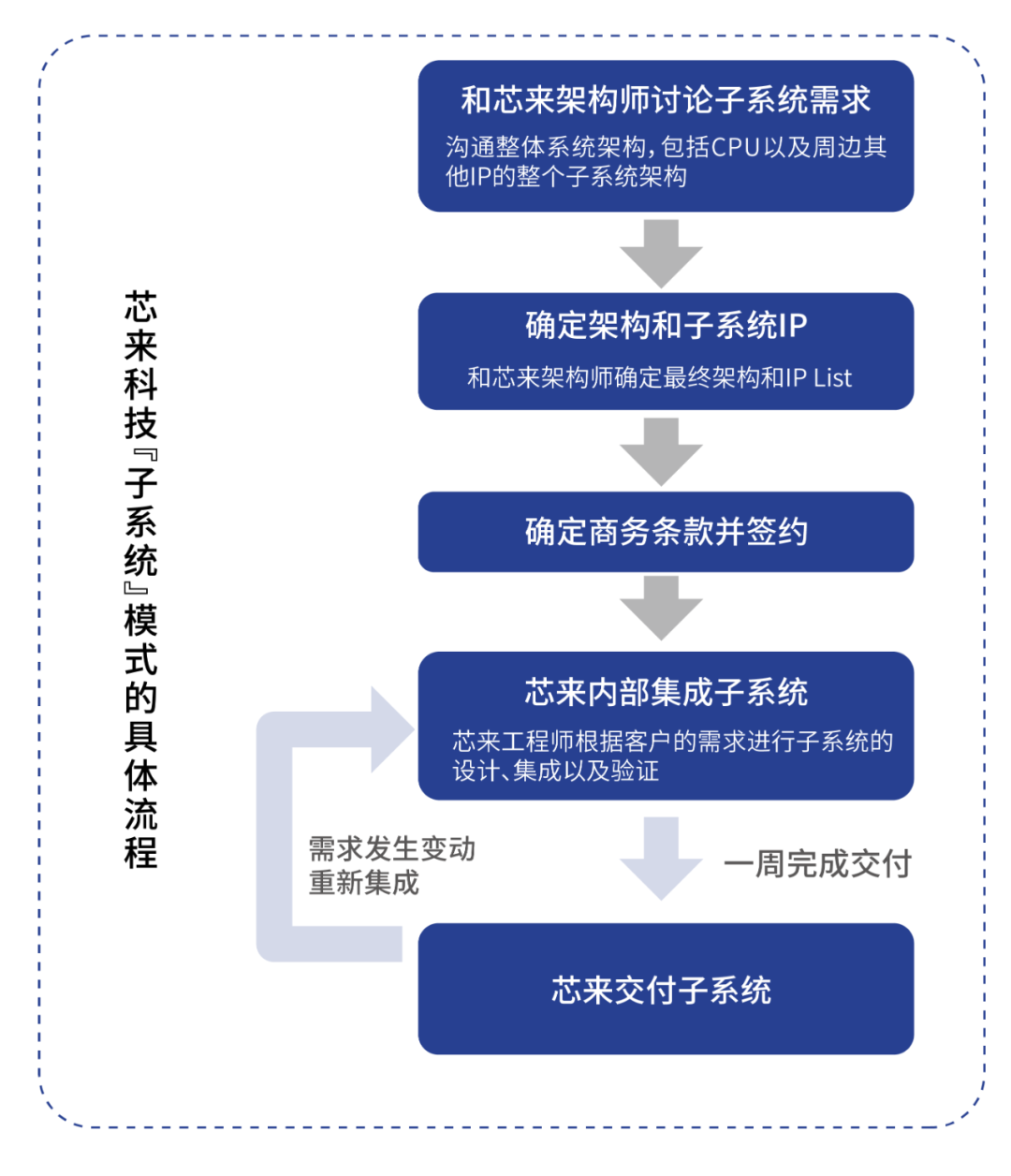

“子系统”模式如何操作?

“子系统”的具体操作模式,如下图所示:

展望:而今迈步从头越

在芯来科技成立六周年之际,芯来科技创始人胡振波表示:

芯来科技成立六年来,在团队建设、技术研发、商业落地、生态构建等方面都取得了一定的突破。

我们基本上追平了与国际上的差距,构建了全球最完备的RISC-V IP产品货架之一;我们支撑了本土大量的RISC-V芯片项目落地,成为了全球范围内客户数量最多的RISC-V IP供应商之一。

芯来科技拥有一支持久稳定且完善的本地化团队,我们将继续秉承专注、中立的专业精神,以RISC-V开放标准为基石,发挥本土的产业链优势,持续推出更多的创新性IP产品,以及持续为‘RISC-V IP 2.0模式’增加更多对本土市场有益的创新性模式。

相关业务咨询

联系电话:+ 86-13886060821

联系邮箱:contact@nucleisys.com

芯来科技从零开始,坚持自研,打造了N/U、NX/UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。其中:

▼往期精彩回顾▼

芯来科技与华东师范大学SOLE实验室合作推动RISC-V性能优化

芯来RISC-V IP引入兆松ZCC工具链,进一步丰富软件生态

芯来、IAR和MachineWare携手加速ASIL标准RV汽车芯片创新

芯来携手西门子EDA,推进RV CPU Trace完整解决方案

芯来携手战略伙伴为RISC-V CPU IP提升DFT可测试性设计

亮相国际舞台 | 芯来RISC-V CPU IP北美峰会引关注